# Eletrônica Digital

## Famílias Lógicas e Circuitos Integrados

Prof. Rômulo Calado Pantaleão Camara Carga Horária: 4h/60h

## Características Básicas de CI Digitais

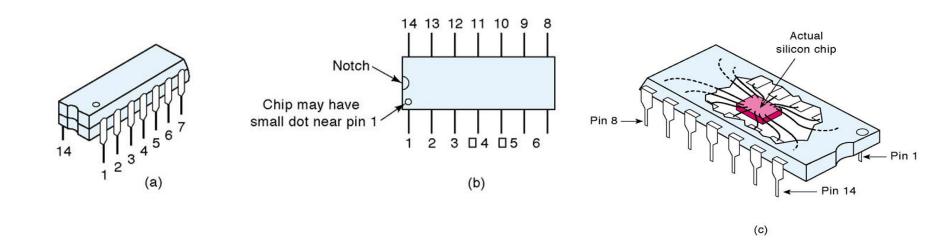

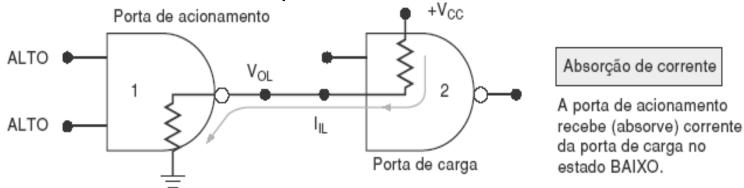

Circuitos Integrados: coleção de componentes fabricados em um único pedaço de material semicondutor (normalmente o silício), normalmente conhecido como chip.

**Chip:** confinado em um encapsulamento protetor plástico ou cerâmico, que possui pinos de conexão com o ambiente externo.

O tipo de encapsulamento mais comum é o DIP (dual in-line package).

## Características Básicas de CI Digitais

#### Vantagens:

- Cls contêm muito mais circuitos em um encapsulamento (menor tamanho comparado aos componentes discretos)

- Custo reduzido para produção em larga escala.

- Redução no número de conexões externas proteção contra solda ruim, interrupção ou curto nas trilhas, etc.

- Redução da potência elétrica para realizar funções digitais quanto menor o transistor, menos dissipação → menos ventilação.

#### **Desvantagens:**

- Não suportam correntes ou tensões elevadas muitos elementos em uma pastilha gera calor acima do limite aceitável

- Certos dispositivos não podem ser implementados em Cls indutores, transformadores e grandes capacitores.

- Componentes discretos ainda são usados nestes casos.

Com a vasta utilização de CIs, é necessário conhecer as suas características elétricas

## Características Básicas de CI Digitais

Família TTL: principal familia de CIs bipolares (utilizam transistores bipolares NPN e PNP) nos ultimos 30 anos.

**Família CMOS:** faz parte de uma classe de CIs unipolares (utilizam transistores unipolares MOSFET canal P ou canal N). Ameaça a liderança dos CIs TTL nas categorias SSI e MSI.

Embora existam diversos fabricantes, a maior parte da nomenclatura de CIs é razoavelmente padronizada.

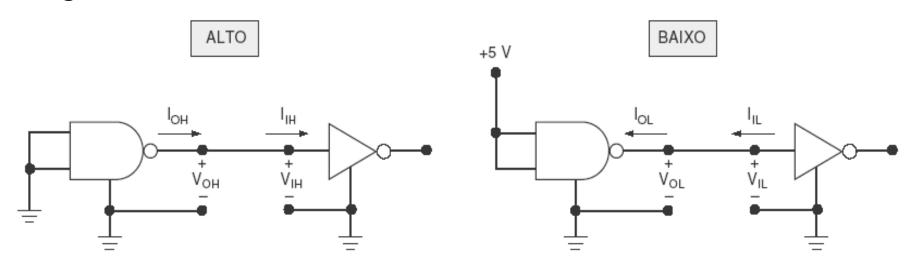

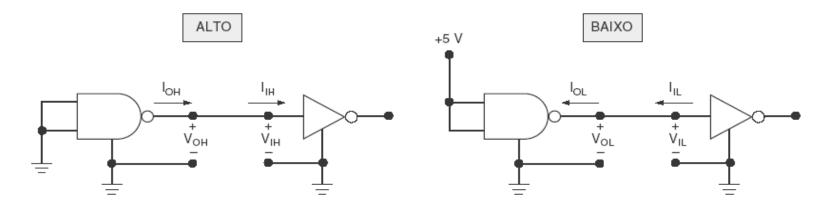

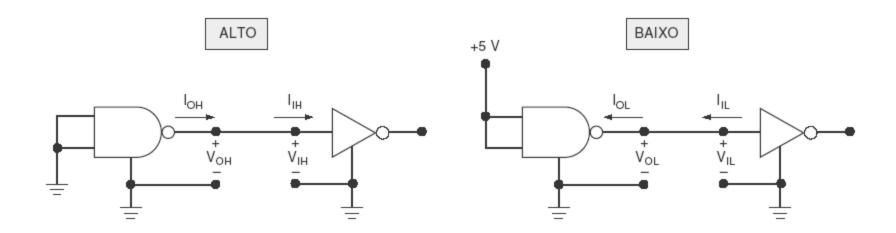

Convenção: A corrente que flui para um nó ou dispositivo é considerada positiva; a corrente que flui para fora de um nó ou dispositivo é considerada negativa.

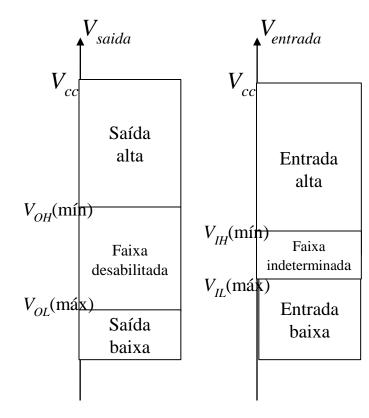

V<sub>IH</sub> (mín) – Tensão de entrada em nível alto. O nível de tensão mínimo requerido para o nível lógico 1 em uma entrada. Valores abaixo desse nível não são interpretados como nível lógico 1.

V<sub>IL</sub> (máx) – Tensão de entrada em nível baixo. O nível máximo de tensão requerido para o nível lógico 0 em uma entrada. Valores acima desse nível não são interpretados como nível lógico 0.

V<sub>OH</sub> (mín) – Tensão de saída em nível alto. O nível de tensão mínimo na saída de um circuito lógico, no estado lógico 1.

V<sub>ol.</sub> (máx) – Tensão de saída em nível baixo. O nível de tensão máximo na saída de um circuito lógico, no estado lógico 0.

Ін — Corrente de entrada em nível alto. A corrente que flui para uma entrada quando uma tensão de nível alto é aplicada naquela entrada.

IIL — Corrente de entrada em nível baixo. A corrente que flui para uma entrada quando uma tensão de nível baixo é aplicada naquela entrada.

**loн — Corrente de saída em nível alto.** A corrente que flui de uma saída em nível alto.

**lo**L – Corrente de saída em nível baixo. A corrente que flui de uma saída em nível baixo.

## Fan-Out (Capacidade de Saída)

Geralmente, Cls são interconectados, de forma que um Cl aciona outro(s) (serve como fonte de corrente ou tensão). Assim, é necessário saber a capacidade de acionamento de uma porta, conhecida como fan-out.

Definição: Número máximo de entradas lógicas que uma saída pode acionar com segurança.

Se este número for excedido, o nível lógico na saída não pode mais ser garantido.

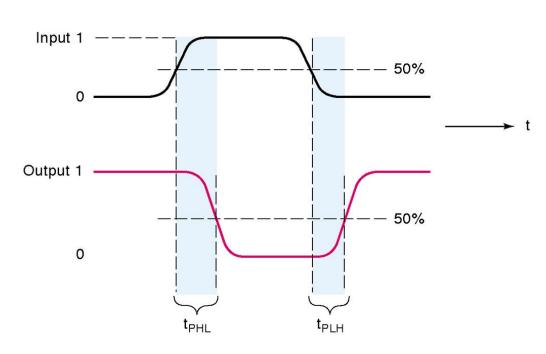

## Atrasos de Propagação

t<sub>PHL</sub> = tempo de atraso do estado lógico 1 para o estado lógico 0.

t<sub>PLH</sub> = tempo de atraso do estado lógico 0 para o estado lógico 1.

- Em geral, os dois atrasos não têm o mesmo valor e variam dependendo das condições de carga.

- Tais atrasos são utilizados como uma medida de velocidade relativa dos circuitos lógicos.

Ex.: Atrasos de propagação para um inversor

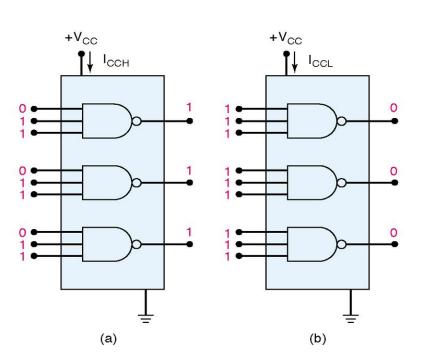

## Requisitos de Potência

A quantidade de potência que um CI necessita é determinada pela corrente ( $I_{CC}$  ou  $I_{DD}$ ) que ele consome da fonte de alimentação ( $V_{CC}$  ou  $V_{DD}$ ), sendo:

Potência =

$$I_{cc} \times V_{cc}$$

Para muitos CIs, a corrente consumida da fonte varia de acordo com os estados lógicos dos circuitos no chip. Em geral  $I_{CCH}$  e  $I_{CCL}$  têm valores diferentes e  $I_{CC}$  média é calculada da seguinte maneira:

$$I_{CC}$$

(média)  $\equiv \frac{I_{CCH} + I_{CCL}}{2}$

$$P_D$$

(média)  $\equiv I_{CC}$  (média)  $\times V_{CC}$

#### Produto Velocidade-Potência

- Cls são caracterizados historicamente tanto pela potência quanto pela velocidade (atraso de propagação e tempo de transição entre níveis lógicos).

- O produto velocidade-potência é uma forma comum para medir e comparar o desempenho de uma família de Cis.

Quanto maior a velocidade, maior a potência dissipada.

**Exemplo:** Para uma família de Cls que tem um atraso médio de propagação de 10 ns e uma dissipação média de potência de 5mW, o produto velocidade-potência é:

10 ns x 5mW =  $50.10^{-12}$  watt-segundo = 50 picojoules (pJ) (1J =  $1w \cdot s$ )

Há um esforço contínuo para reduzir o produto velocidade – potência, o que é difícil devido à natureza dos circuitos de chaveamento.

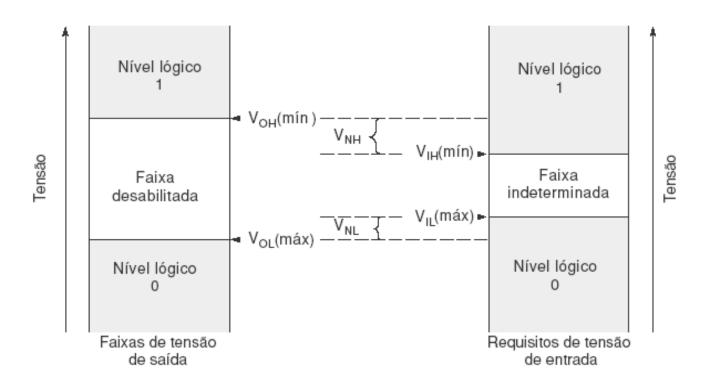

#### Imunidade ao Ruído

- Campos elétricos e magnéticos parasitas podem induzir tensões nas conexões entre circuitos lógicos, assim como interferências de circuitos externos.

- Os sinais espúrios indesejáveis são chamados de ruído, que podem levar valores de tensão para longe dos níveis aceitáveis.

- A imunidade ao ruído de um circuito lógico é a capacidade de tolerância a ruídos sem alteração dos níveis lógicos de saída.

- Margem de ruído: medida quantitativa da imunidade ao ruído de um circuito lógico.

#### Imunidade ao Ruído

A margem de ruído aplica-se a conexões entre dois circuitos digitais para um dos dois níveis (ALTO ou BAIXO).

- A margem de ruído para o estado alto (VNH) é definida como:

VNH = VOH(mín) - VIH(mín) → suporta spikes de ruído negativo até VNH

- A margem de ruído para o estado baixo (VNL) é definida como:

VNL = VIL(máx) - VoL(máx) → suporta spikes de ruído positivo até VNL

#### Imunidade ao Ruído

Exemplo: Um dispositivo lógico tem as seguintes especificações:  $V_{OH}(mín) = 2,4V$ ,  $V_{OI}(máx) = 0,4V$ ,  $V_{IH}(mín) = 2,0V$  e  $V_{II}(máx) = 0,8V$ . Determine:

- a) a maior amplitude de ruído tolerável quando uma saída nível ALTO está acionando uma entrada.

- b) a maior amplitude de ruído tolerável quando uma saída nível BAIXO está acionando uma entrada.

#### Solução:

a) Saída nível ALTO acionando entrada pode ser tão baixa quanto  $V_{OH}(mín) = 2,4V$  e a entrada acionada responderá a uma tensão não menor que  $V_{IH}(mín) = 2,0V$ . Desta forma, a maior amplitude de ruído será:

$$V_{NH} = V_{OH}(min) - V_{IH}(min) = 0.4V$$

b) Saída em nível BAIXO pode ser tão alta quanto  $V_{OL}(máx) = 0.4V$  e entrada responderá a tensões não maiores que  $V_{IL}(máx) = 0.8V$ . Assim, a maior amplitude de ruído será:

$$V_{NL} = V_{IL}(m\acute{a}x) - V_{OL}(m\acute{a}x) = 0.4V$$

#### Níveis de Tensão Inválidos

Para operação lógica correta, os níveis de tensão devem estar fora da faixa indeterminada, ou seja, níveis acima de  $V_{IH}(mín)$  ou abaixo de  $V_{IL}(máx)$ .

Para valores contidos na faixa indeterminada, a entrada é inválida e produzirá uma resposta de saída imprevisível.

- Em condições normais (circuitos operando dentro das especificações) não se atinge a região inválida.

- Caso contrário, tem-se entradas inválidas quando:

- A saída lógica tem problemas.

- Opera com sobrecarga (fan-out excedido).

- Tensões de alimentação fora da faixa aceitável.

- O dispositivo do exemplo anterior funcionará com um nível de entrada de 1,7V?

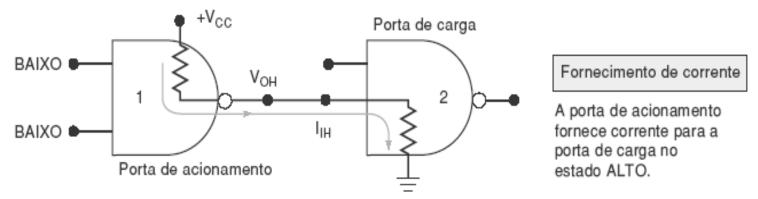

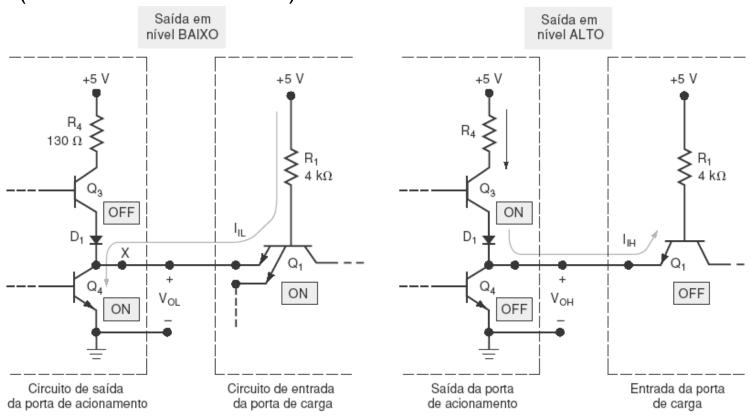

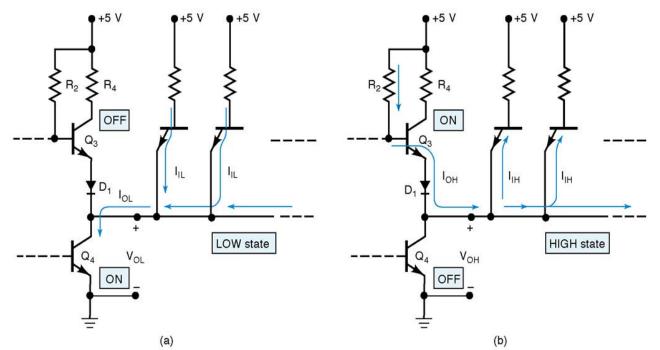

## Ação de Fornecimento e de Absorção de Corrente

Pode-se descrever circuitos lógicos pelo modo como a corrente flui de um circuito a outro:

• Quando a saída da porta número 1 está em nível lógico ALTO, ela **fornece** uma corrente IIH para a entrada da porta número 2.

• Quando a saída da porta número 1 está em nível lógico BAIXO, ela **absorve** uma corrente lu da porta número 2.

## Encapsulamento de Circuitos Integrados

- As famílias lógicas distinguem-se umas das outras pelo tipo de dispositivo semicondutor incorporados e pela forma como estes dispositivos são interligados.

- A Lógica Transistor-Transistor (TTL) é uma série original de dispositivos lógicos, que existe há mais de 30 anos, e foi introduzida em 1964 pela Texas Instruments

- Utiliza transistores de junção bipolares (TJB).

- Apesar de gradativamente substituída por outras famílias, ainda é amplamente utilizada como lógica auxiliar ou que necessitem de acionamentos com altas correntes.

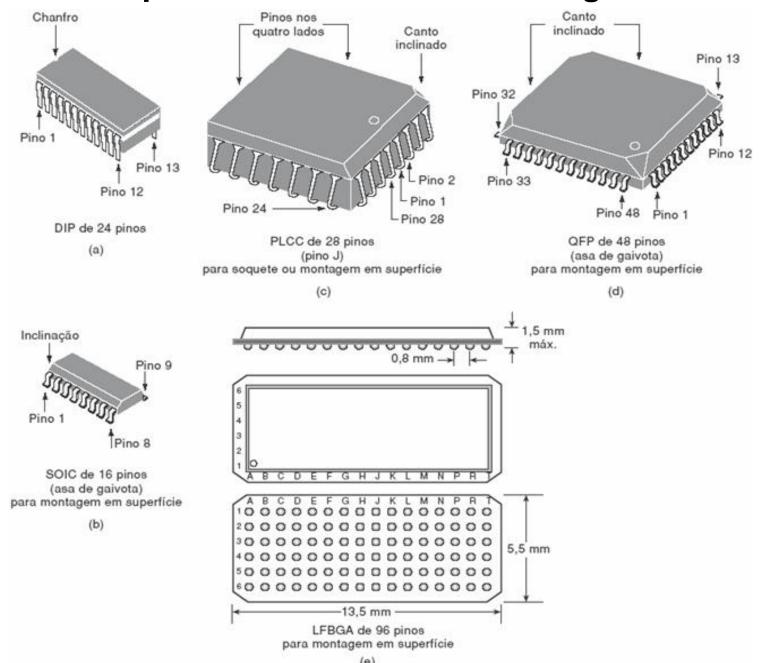

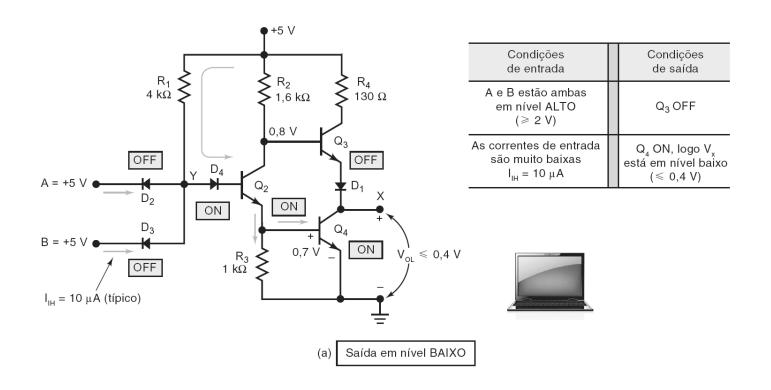

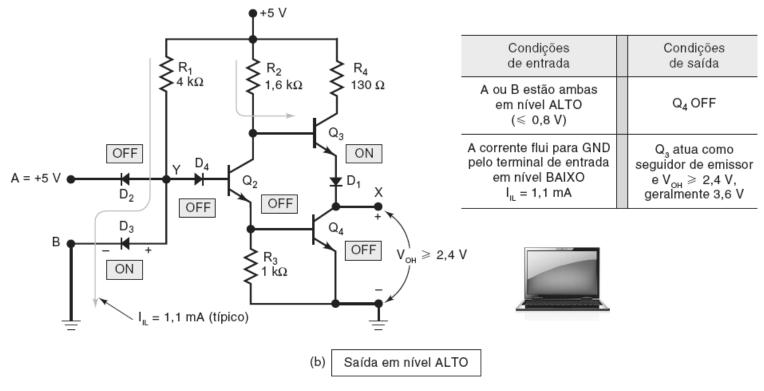

### O circuito TTL básico e a porta NAND.

- As características de entrada das famílias TTL são provenientes do transistor Q1 (múltiplos emissores ate 8).

- A ou B em  $0 \Longrightarrow Q1$  (conduz), Q2 (corta), Q3 (conduz) e Q4 (corta).

- A e B em 1 → Q1 (corta), Q2 (conduz), Q3 (corta) e Q4 (conduz).

Totem-pole: dois transistores que operam como chave, sempre com um ou outro conduzindo.

Alta velocidade para tempos de subida.

Usada para manter baixa a dissipação media de potencia.

Portas TTL NAND com saída nível baixo

Portas TTL NAND com saída nível ALTO

FIGURA 8.8 Porta NANDTTL nos seus dois estados de saída.

## Absorção e Fornecimento de Corrente

- Q4 atua como absorvedor de corrente (drenando sua corrente da carga).

- Q3 atua com fornecedor de corrente (fornecendo corrente para a carga).

- Q4 é chamado de transistor de absorção de corrente ou transistor pull-down (conecta a saída ao terra).

- Q3 é chamado de transistor de fornecimento de corrente ou transistor pull-up (conecta a saída a Vcc).

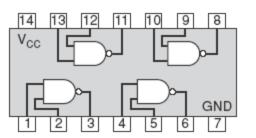

Todos os fabricantes de CIs TTL usam o mesmo sistema de número de identificação, seguindo o precursor Texas Instruments (séries 54 e 74).

Fabricantes distintos usam prefixos especiais próprios, tais como:

#### - Chip quádruplo de portas NAND.

DM7400 - National Semiconductor;

SN7400 – Texas Instruments;

S7400 – Signetics.

**Família TTL:** 74, 74LS, 74S, etc. Séries diferem nas características que definem as capacidades e limitações desses dispositivos.

Todas as informações a respeito dos CIs podem ser encontradas na folha de dados (*data sheet*) editadas pelos fabricantes.

Como exemplo, considere o 54/74ALS00, com quatro portas NAND de duas entradas.

## Folha de Dados (data sheet) 54/74ALS00

#### recommended operating conditions

|     |                                | SN  | SN54ALS00A |      | SN74ALS00A |            |      |      |

|-----|--------------------------------|-----|------------|------|------------|------------|------|------|

|     |                                | MIN | NOM        | MAX  | MIN        | NOM        | MAX  | UNIT |

| Vcc | Supply voltage                 | 4.5 | 5          | 5.5  | 4.5        | 5          | 5.5  | ٧    |

| VIH | High-level input voltage       | 2   |            |      | 2          |            |      | V    |

| VIL | Low-level input voltage        |     |            | 0.8‡ | 1          | Vert 1 - 1 | 0.8  | v    |

|     |                                |     |            | 0.7§ |            |            |      | 1 °  |

| ЮН  | High-level output current      |     |            | -0.4 |            |            | -0.4 | mA   |

| loL | Low-level output current       |     |            | 4    |            |            | 8    | mA   |

| TA  | Operating free-air temperature | -55 |            | 125  | 0          |            | 70   | °C   |

<sup>\$</sup> Applies over temperature range -55°C to 70°C

## electrical characteristics over recommended operating free-air temperature range unless otherwise noted)

| PARAMETER | TEST CONDITIONS                             |                            | SN54ALS00A         |      |            | SN74ALS00A         |      |      |      |

|-----------|---------------------------------------------|----------------------------|--------------------|------|------------|--------------------|------|------|------|

| PARAMETER |                                             |                            | MIN                | TYPT | MAX        | MIN                | TYPT | MAX  | UNIT |

| VIK       | V <sub>CC</sub> = 4.5 V,                    | I <sub>I</sub> = -18 mA    |                    |      | -1.2       |                    |      | -1.5 | V    |

| VOH       | $V_{CC} = 4.5 \text{ V to } 5.5 \text{ V},$ | $I_{OH} = -0.4 \text{ mA}$ | V <sub>CC</sub> -2 |      |            | V <sub>CC</sub> -2 |      |      | V    |

| VOL       | V <sub>CC</sub> = 4.5 V                     | I <sub>OL</sub> = 4 mA     |                    | 0.25 | 0.4        |                    | 0.25 | 0.4  | v    |

| VOL       | VCC - 4.5 V                                 | I <sub>OL</sub> = 8 mA     | 3 0 -153           |      | Maria ya S |                    | 0.35 | 0.5  | ٧    |

| II        | V <sub>CC</sub> = 5.5 V,                    | V <sub>I</sub> = 7 ∨       |                    |      | 0.1        |                    |      | 0.1  | mA   |

| Iн        | V <sub>CC</sub> = 5.5 V,                    | V <sub>I</sub> = 2.7 V     | -100               |      | 20         |                    |      | 20   | μА   |

| IIL       | V <sub>CC</sub> = 5.5 V,                    | V <sub>I</sub> = 0.4 V     |                    |      | -0.1       |                    |      | -0.1 | mA   |

| 10‡       | V <sub>CC</sub> = 5.5 V,                    | V <sub>O</sub> = 2.25 V    | -20                |      | -112       | -30                |      | -112 | mA   |

| Іссн      | V <sub>CC</sub> = 5.5 V,                    | V <sub>I</sub> = 0         |                    | 0.5  | 0.85       |                    | 0.5  | 0.85 | mA   |

| ICCL.     | V <sub>CC</sub> = 5.5 V.                    | V <sub>I</sub> = 4.5 V     |                    | 1.5  | 3          |                    | 1.5  | 3    | mA   |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC}$  = 5 V,  $T_A$  = 25°C.

#### switching characteristics (see Figure 1)

| PARAMETER | FROM<br>(INPUT)                          | TO<br>(OUTPUT) | V <sub>CC</sub> = 4.5 V to 5.5 V,<br>C <sub>L</sub> = 50 pF,<br>R <sub>L</sub> = 500 Ω,<br>T <sub>A</sub> = MIN to MAX§ |       |       |     | UNIT |

|-----------|------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------|-------|-------|-----|------|

|           | , ,                                      | ,              | SN54ALS00A SN74                                                                                                         | SN74A | LS00A |     |      |

|           | 19 19 19 19 19 19 19 19 19 19 19 19 19 1 |                | MIN                                                                                                                     | MAX   | MIN   | MAX |      |

| tPLH      | A or D                                   |                | 3                                                                                                                       | 15    | 3     | 11  |      |

| tPHL .    | A or B                                   | 1              | 2                                                                                                                       | 9     | 2     | 8   | ns   |

<sup>§</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

<sup>§</sup> Applies over temperature range 70°C to 125°C

<sup>&</sup>lt;sup>‡</sup> The output conditions have been chosen to produce a current that closely approximates one half of the true short-circuit output current, IOS.

#### Faixas de Tensão de Alimentação

Ambas as séries usam tensão de alimentação nominal Vcc = 5 V, podendo tolerar variações de ±0,5 V.

Série 74ALS – projetada para 0 a 70°C (aplicações comerciais)

Série 54ALS – projetada para -55 a +125°C (aplicações militares/espaciais)

#### Níveis de Tensão

Os valores mostrados representam o pior caso de tensão de alimentação, temperatura e condições de acionamento de carga.

$$V_{NL} = V_{IL}(max) - V_{OL}(max) = 0.8 - 0.5 = 0.3 V$$

$$V_{NH} = V_{OH}(mim) - V_{IH}(mim) = 2.5 - 2 = 0.5 V$$

Como forma de comparação, costuma-se usar a margem de ruído garantida para o pior caso da série 74ALS, que é de 0,3 V.

#### Dissipação de Potência Nominal

Consumo médio de cada porta NAND TTL = 2,4 mW.

$$I_{CC}(méd) = (I_{CCH} + I_{CCL}) / 2 = (0.85 + 3) \text{ mA} / 2 = 1.925 \text{ mA}.$$

$$P_D(méd)_{chip} = 1,925 \text{ mA x 5 V} = 9,65 \text{ mW (potência total das 4 portas do chip)}.$$

$$P_D(méd)_{porta} = 9,65 \text{ mW} / 4 = 2,4 \text{ mW (por porta)}.$$

#### Atrasos de Propagação

Adotar a média dos valores máximo e mínimo:  $t_{PLH} = (11+3)/2 = 7$  ns e  $t_{PHL} = (8+2)/2 = 5$  ns.

O atraso de propagação médio típico é de  $t_{pd} = (t_{PHL} + t_{PLH})/2 = 6$  ns.

**Opcionalmente:**  $t_{pd} = max \{t_{PHL} e t_{PLH}\}$

**Exemplo:** Observando o *data sheet* do 74ALS00, determine a potência de dissipação média máxima e o atraso de propagação médio máximo para uma porta NAND.

Solução: Devemos encontrar  $P_{med}(máx)_{porta} = I_{CCmed}(máx) \times V_{CC}(máx) / 4$ . A corrente é obtida tomando-se a média dos valores máximos de  $I_{CCH}$  e  $I_{CCL}$ . Pelo *data sheet*, vemos que

$$I_{CCmed}(máx) = (I_{CCH}(máx) + I_{CCL}(máx)) / 2 = (0.85 + 3) / 2 = 1.925 \text{ mA}$$

Também pelo data sheet, vemos que esses valores foram obtidos quando  $V_{CC} = 5,5V$ . Portanto:

$$P_{\text{med}}(\text{máx})_{\text{porta}} = I_{\text{CCmed}}(\text{máx}) \times V_{\text{CC}}(\text{máx}) / 4 = 1,925 \text{ mA} \times 5,5 \text{ V} / 4 = 2,65 \text{ mW}$$

Os atrasos de propagação máximos são t<sub>PLH</sub> = 11 ns e t<sub>PHL</sub> = 8 ns, o que dá:

$$t_{PD}$$

(máx) = (11 + 8) / 2 = 9,5 ns

## Comparação entre séries TTL

|                          | 74  | 74S | 74LS | 74AS | 74ALS | 74F |

|--------------------------|-----|-----|------|------|-------|-----|

| Índice de Desempenho     |     |     |      |      |       |     |

| Atraso de Propagação     | 9   | 3   | 9,5  | 1,7  | 4     | 3   |

| Diss. de Potência (mW)   | 10  | 20  | 2    | 8    | 1,2   | 6   |

| Velocidade-potência (pJ) | 90  | 60  | 19   | 13,6 | 4,8   | 18  |

| Taxa Máx. Clock (MHz)    | 35  | 125 | 45   | 200  | 70    | 100 |

| Fan-Out (mesma série)    | 10  | 20  | 20   | 40   | 20    | 33  |

| Parâmetros de Tensão     |     |     |      |      |       |     |

| VOH(mín)                 | 2,4 | 2,7 | 2,7  | 2,5  | 2,5   | 2,5 |

| VOL(máx)                 | 0,4 | 0,5 | 0,5  | 0,5  | 0,5   | 0,5 |

| VIH(mín)                 | 2,0 | 2,0 | 2,0  | 2,0  | 2,0   | 2,0 |

| VIL(máx)                 | 0,8 | 0,8 | 0,8  | 0,8  | 0,8   | 0,8 |

Valores tipicos para as caracteristicas mais importantes de cada uma das series TTL.

## Comparação entre séries TTL

**Exemplo:** Usando a tabela anterior, calcule as margens de ruído para um 74LS típico.

#### Solução:

$$VNH = VOH(min) - VIH(min) = 2,7 - 2,0 = 0,7 V$$

$$VNL = VIL(máx) - VOL(máx) = 0.8 - 0.5 = 0.3 V$$

**Exemplo:** Qual das séries pode acionar o maior número de portas da mesma série?

Resposta: Série 74AS, pois tem o maior fan-out = 40.

## Fan-Out e Acionamento de Carga para TTL

**BAIXO** - Quando Q4 conduz ele absorve corrente. Devido à sua resistência coletor/emissor, se IOL for alta (muitas portas conectadas à saída) VOL pode exceder o limite de VOL(máx) e reduzir a margem de ruído. Se VOL ultrapassa VIL(máx) ela estará na faixa indeterminada.

**ALTO** – Quando Q3 conduz ele fornece corrente. Se IOH for muito alta haverá um aumento da queda de tensão em R2, podendo levar VOH abaixo de VOH(mín), reduzindo a margem de ruído. Se VOH ultrapassa VIH(mín) ela estará na faixa indeterminada.

Em resumo, IOH(máx) e IOL(máx) limitam o número de portas conectadas.

#### **Determinando o fan-out**

Quantas portas NAND 74ALS00 podem ser acionadas pela saída de uma porta NAND 74ALS?

#### Observando o datasheet:

#### **Nível BAIXO**

$I_{OL(m\acute{a}x)} = 8$  mA e  $I_{IL(m\acute{a}x)} = -0.1$  mA (corrente negativa  $\rightarrow$  flui para fora do terminal de entrada; pode-se ignorá-lo para o propósito atual)

fan-out (0) =

$$I_{OL(m\acute{a}x)} / I_{IL(m\acute{a}x)} = 80$$

#### **Nível ALTO**

$$I_{OH(m\acute{a}x)} = -400 \text{ uA e } I_{IH(m\acute{a}x)} = 20 \text{ uA} \rightarrow \text{fan-out } (1) = I_{OH(m\acute{a}x)} / I_{IH(m\acute{a}x)} = 20$$

$fan-out = minimo\{fan-out (0), fan-out (1)\} = 20$

#### **Determinando o fan-out**

Quando aparece combinação de varias famílias lógicas:

- 1- **Some o IIH** para todas as entradas que estão conectadas a uma saída. Essa soma tem que ser menor do que a especificação do IOH da saída.

- 2 **Some o IIL** para todas as entradas que estão conectadas a uma saída. Essa soma tem que ser menor do que a especificação do IOL da saída.

**Exemplo:** Determine se ha problema em uma porta 74ALS00 acionar três portas 74S00 e uma 7400.

**Soma de IIH** =  $3 \times 50 \text{ uA} + 1 \times 40 \text{ uA} = 190 \text{ uA} < 400 \text{ uA}$  (IOH do 74ALS00) – nível alto OK.

**Soma de IIL** =  $3 \times 2 \text{ mA} + 1 \times 1,6 \text{ mA} = 7,6 \text{ mA} < 8 \text{ mA} (IOL do 74ALS00) – nivel baixo OK.$

|       | Saída    | Saída    | Entrada  | Entrada  |

|-------|----------|----------|----------|----------|

| TTL   | Iон (mA) | Iol (mA) | IIH (uA) | IIL (mA) |

| 74    | - 0,4    | 16       | 40       | - 1,6    |

| 74S   | - 1      | 20       | 50       | - 2      |

| 74LS  | - 0,4    | 8        | 20       | - 0,4    |

| 74AS  | - 2      | 20       | 20       | - 0,5    |

| 74ALS | - 0,4    | 8        | 20       | - 0,1    |

| 74F   | - 1      | 20       | 20       | - 0,6    |

#### **Determinando o fan-out**

**Exemplo:** A saída da porta 74ALS00 do exemplo anterior precisa ser usada para acionar, além das portas descritas, algumas portas 74ALS. Quantas destas portas podem ser acionadas a mais, sem causar sobrecarga?

De acordo com o exemplo anterior, o nível baixo esta mais próximo de uma sobrecarga.

Portanto, vamos avaliá-lo.

A corrente da carga já acionada e 7,6 mA (soma das IIL). A porta 74ALS00 pode fornecer ate 8 mA (IOL(max)), portanto, ha uma 'sobra' de 0,4 mA. Como cada entrada da 74ALS demanda IIL de 0,1 mA, podemos conectar mais 4 portas 74ALS a saída da porta 74ALS00 sem causar sobrecarga.

|       | Saída    | Saída    | Entrada  | Entrada  |

|-------|----------|----------|----------|----------|

| TTL   | Iон (mA) | IOL (mA) | IIH (uA) | IIL (mA) |

| 74    | - 0,4    | 16       | 40       | - 1,6    |

| 74S   | - 1      | 20       | 50       | - 2      |

| 74LS  | - 0,4    | 8        | 20       | - 0,4    |

| 74AS  | - 2      | 20       | 20       | - 0,5    |

| 74ALS | - 0,4    | 8        | 20       | - 0,1    |

| 74F   | - 1      | 20       | 20       | - 0,6    |

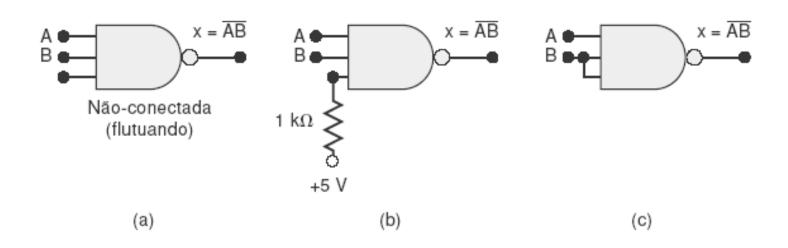

#### **Outras Características TTL**

- Entradas em aberto (flutuando) = nível 1

- Entradas não utilizadas devem ser tratadas por uma das técnicas:

- (a) Realiza a função desejada, mas atua como antena;

- (b) Melhor técnica. O resistor protege entrada contra spikes da fonte;

- (c) Funciona bem, desde que o fan-out do circuito acionador da entrada B não seja excedido.

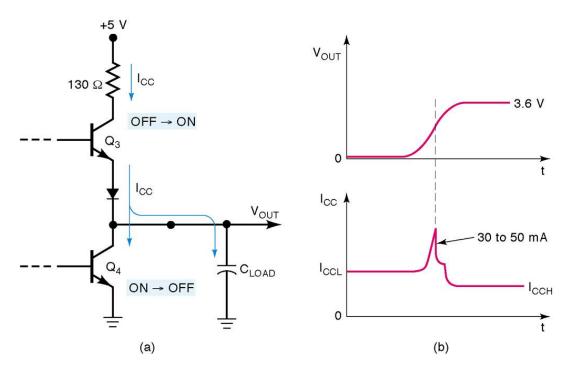

#### **Transientes de Corrente**

Sempre que uma saída TTL totem-pole vai de nível baixo para nível alto, um pico de corrente de alta amplitude é drenado da fonte de alimentação.

- Surto de corrente é de aproximadamente 30 a 50 mA.

- ➤ Pior se existem várias saídas comutando ao mesmo tempo (vários spikes).

- ➤ Uma solução é instalar pequenos capacitores entre Vcc e GND (desacoplamento da fonte de alimentação).

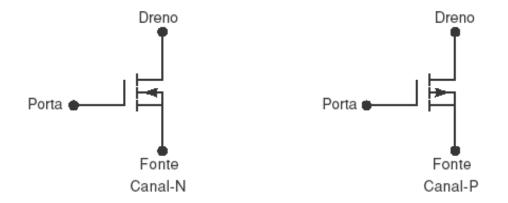

## TECNOLOGIA MOS (Semicondutor de Óxido Metálico)

Transistores implementados com tecnologia MOS são transistores de efeito de campo denominados MOSFET.

#### **Principais vantagens:**

- Relativamente simples a fabricação apresenta 1/3 da complexidade dos CIs bipolares (TTL, ECL, etc);

- Pequenos ocupam menos espaço no chip do que os CIs bipolares, que usam elementos resistores que ocupam uma grande área no chip.

- Dispositivos MOS estão cada vez mais rápidos dominando também o mercado SSI e MSI.

#### **Desvantagem:**

• Susceptibilidade de danos por eletricidade estática.

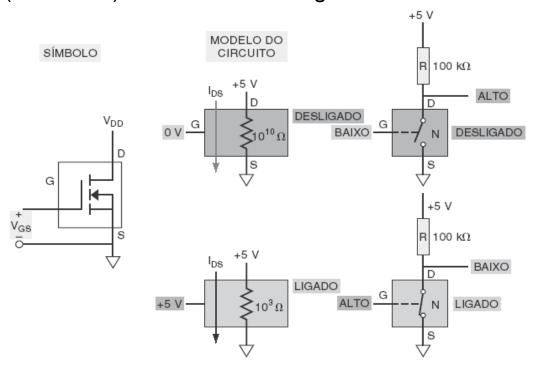

### **O MOSFET**

Os Cls MOS usam exclusivamente MOSFET do tipo enriquecimento, que serão analisados como chaves liga / desliga.

Linha tracejada indica que normalmente não há condução entre dreno e fonte.

Separação da porta indica alta resistência (~ 10<sup>12</sup> Ohm)

Os CI MOSFET são classificados em três categorias:

- 1- P-MOS, que usa apenas MOSFET canal P tipo enriquecimento

- 2- N-MOS, que usa apenas MOSFET canal N tipo enriquecimento

- 3- CMOS (MOS complementar), que usa os dispositivos canal P e canal N.

### **O MOSFET**

VGS controla a resistência entre dreno e fonte, determinando se o dispositivo está ligado ou desligado.

N-MOS

VGS BAIXO (entrada 0) → MOSFET desligado

VGS ALTO (entrada 1) → MOSFET ligado

P-MOS tem lógica de acionamento invertida, i.e.:

VGS BAIXO (entrada 0) → MOSFET ligado

VGS ALTO (entrada 1) → MOSFET desligado

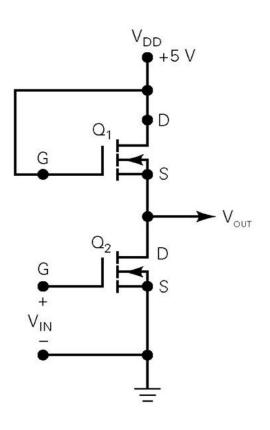

# **Inversor MOSFET**

# Q1 funciona como resistor de pull-up ~100 kOhm

| V <sub>IN</sub>                |  | Q <sub>1</sub>                 | $Q_2$                                        | V <sub>OUT</sub>   |  |

|--------------------------------|--|--------------------------------|----------------------------------------------|--------------------|--|

| +V <sub>DD</sub><br>(lógico 1) |  | OFF $R_{OFF} = 10^{10} \Omega$ | ON<br>R <sub>ON</sub> = 1 kΩ                 | ≃ 0 V              |  |

| 0 V<br>(lógico 0)              |  |                                | OFF<br>R <sub>OFF</sub> = 10 <sup>10</sup> Ω | ≃ +V <sub>DD</sub> |  |

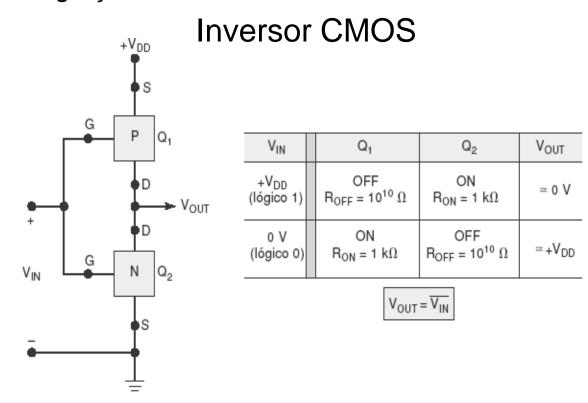

# Lógica MOS Complementar (CMOS)

- A família lógica CMOS utiliza MOSFET tanto canal N quanto canal P para obter diversas vantagens sobre as famílias N-MOS e P-MOS.

- CMOS consome menos potência e são mais rápidos do que as demais famílias MOS.

- Contrapartida: aumento de complexidade de fabricação do CI e menor densidade de integração.

# Lógica MOS Complementar (CMOS)

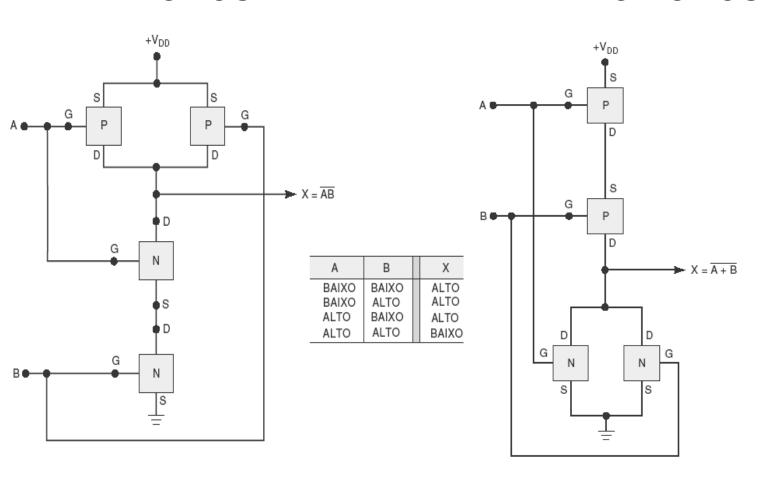

# NAND CMOS

# NOR CMOS

| Α     | В     | Х     |

|-------|-------|-------|

| BAIXO | BAIXO | ALTO  |

| BAIXO | ALTO  | BAIXO |

| ALTO  | BAIXO | BAIXO |

| ALTO  | ALTO  | BAIXO |

- •Família CMOS: 4000, 74HC/HCT, 74AC/ACT, etc. Diferem nas caracteristicas.

- Níveis de Tensão

Os niveis de tensao de entrada e saida sao diferentes para cada serie.

Margens de Ruído

Em geral, os CIs CMOS possuem margens de ruido maiores que os TTL.

|        | CMOS  | CMOS | CMOS         | CMOS | CMOS  | CMOS          | CMOS   | TTL | TTL  | TTL  | TTL   |

|--------|-------|------|--------------|------|-------|---------------|--------|-----|------|------|-------|

|        | 4000B | 74HC | <b>74HCT</b> | 74AC | 74ACT | <b>74AH</b> C | 74AHCT | 74  | 74LS | 74AS | 74ALS |

| VIHmín | 3,5   | 3,5  | 2,0          | 3,5  | 2,0   | 3,85          | 2,0    | 2,0 | 2,0  | 2,0  | 2,0   |

| VILmáx | 1,5   | 1,0  | 0,8          | 1,5  | 0,8   | 1,65          | 0,8    | 0,8 | 0,8  | 0,8  | 0,8   |

| VoHmín | 4,95  | 4,9  | 4,9          | 4,9  | 4,9   | 4,4           | 3,15   | 2,4 | 2,7  | 2,7  | 2,5   |

| Volmin | 0,05  | 0,1  | 0,1          | 0,1  | 0,1   | 0,44          | 0,1    | 0,4 | 0,5  | 0,5  | 0,5   |

| VNH    | 1,45  | 1,4  | 2,9          | 1,4  | 2,9   | 0,55          | 1,15   | 0,4 | 0,7  | 0,7  | 0,7   |

| Vnl    | 1,45  | 0,9  | 0,7          | 1,4  | 0,7   | 1,21          | 0,7    | 0,4 | 0,3  | 0,3  | 0,4   |

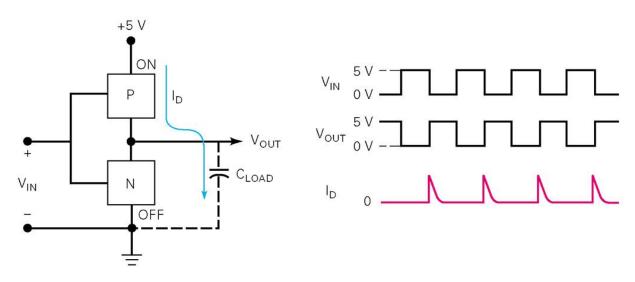

# Dissipação de Potência

- Quando um CI CMOS não está comutando, sua dissipação de potência é extremamente baixa (PD = 2,5 nW por porta).

- A dissipação de potência aumenta proporcionalmente com a frequência, por exemplo (VDD = 10 V):

PD = 10 nW em condições CC; PD = 0,1 mW com f = 100 kpps; PD=1 mW com f = 1MHz.

- Se f aumenta, o número de pulsos e a corrente média drenada de VDD também aumenta.

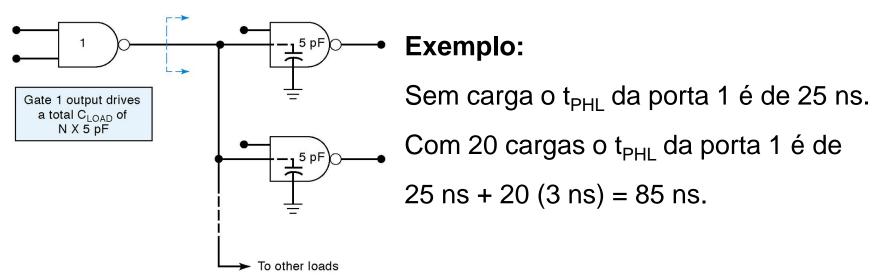

#### Fan-out

- As entradas CMOS possuem uma resistência muito alta (10<sup>12</sup> Ohms) e drenam uma corrente muito pequena.

- Cada entrada CMOS apresenta uma carga de 5 pF para GND, que limita o n° de entradas acionadas.

- Normalmente, cada entrada aumenta o atraso de propagação do circuito acionador em 3 ns.

- Fan-out depende do atraso de propagação máximo.

- Geralmente 50 para freq. < 1MHz.</li>

#### Entradas não usadas

As entradas CMOS nunca devem ficar desconectadas.

#### Sensibilidade à eletricidade estática

- Dispositivos CMOS são mais susceptíveis a descargas eletrostáticas.

- Diferença de potencial cria corrente na camada óxida, danificando o elemento.

- Deve-se ter cuidado ao manusear CIs CMOS.

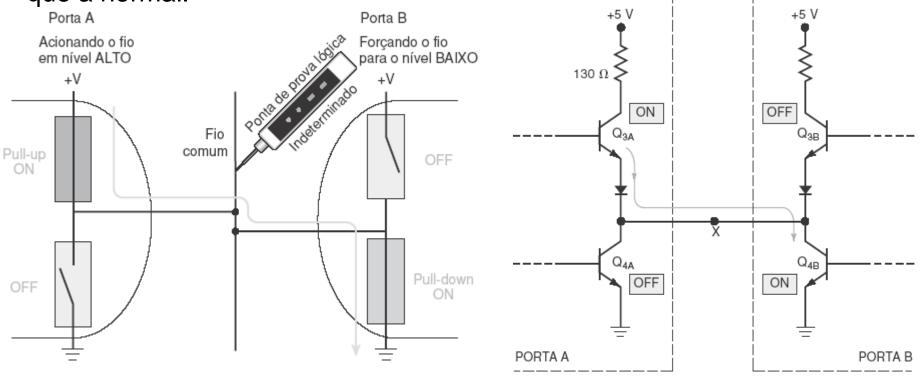

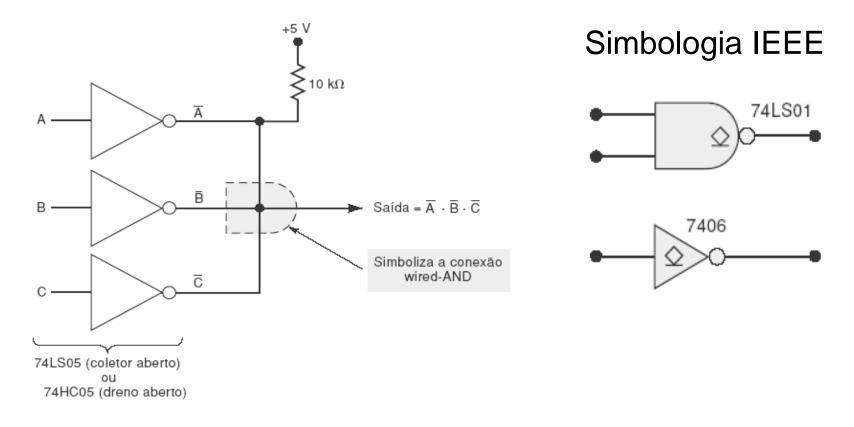

### Saída em Coletor Aberto

Situação: compartilhamento de uma via (fio).

As saídas de circuitos convencionais (CMOS ou TTL) nunca devem ser conectadas juntas.

Os transistores de pull-up e pull-down terão uma corrente muito maior

que a normal.

Em ambos os casos (CMOS = VDD/2 e TTL ~ 1V) o nível de saída estará na faixa indeterminada.

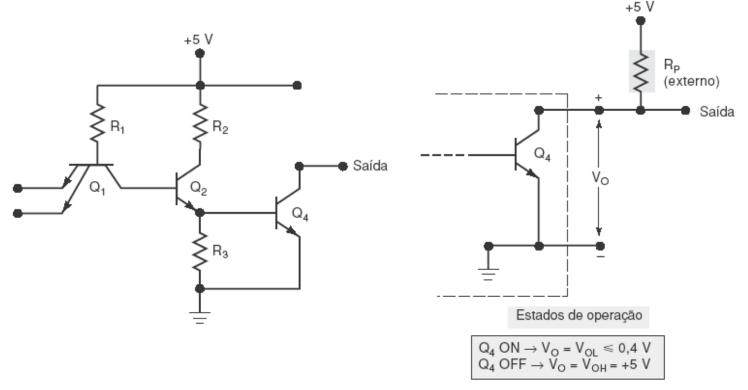

# Saída em Coletor Aberto

- A solução para o compartilhamento da via é remover o transistor pull-up ativo do circuito de saída de cada porta, fazendo com que nenhuma porta insista no nível lógico alto.

- Os circuitos CMOS assim modificados são chamados de "saídas de dreno aberto", enquanto os circuitos TTL "saídas de coletor aberto".

Neste caso, um resistor Rp (pull-up) deve ser conectado para estabelecer o nível alto (~ 10 kOhm).

## Saída em Coletor Aberto

- Quando várias portas com saídas de coletor (ou dreno) aberto compartilham uma conexão em comum, a saída estará em nível baixo quando qualquer uma das saídas estiver em nível baixo wired-AND.

- Os dispositivos de coletor aberto são lentos no chaveamento de nível baixo para nível alto e, portanto, não são usados em aplicações de alta velocidade.

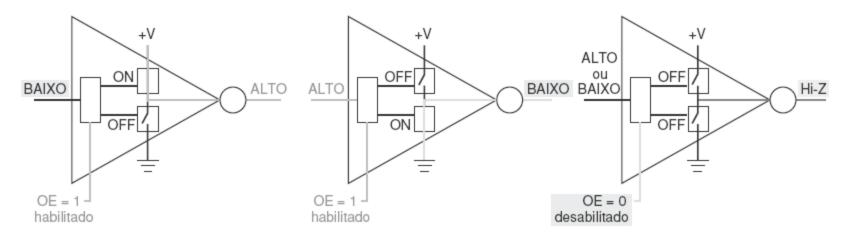

# Saídas Lógicas Tristate (Três Estados)

- Circuito de saída usado nas famílias TTL e CMOS.

- Aproveita a operação em alta velocidade da configuração totem-pole, permitindo que as saídas compartilhem um fio comum.

- Permite três estados: ALTO, BAIXO e ALTA IMPEDÂNCIA (Hi-Z) transistores de saída (pull-up e pull-down) desligados.

- A entrada *enable* (E) ou *output enable* (OE) determina se a porta está em funcionamento normal ou em alta impedância.

- OE = 1, circuito em operação normal

- OE = 0, circuito em Hi-Z (ambos os transistores em corte)

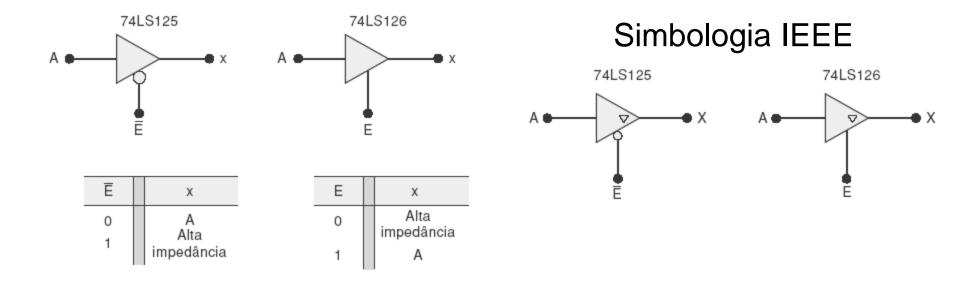

## Saídas Tristate

- As saídas podem ser conectadas juntas sem sacrificar a velocidade.

- Apenas uma saída deve ser habilitada de cada vez, caso contrário haverá conflito de nível lógico.

#### **Buffer Tristate**

Circuito utilizado para controlar a passagem do sinal lógico da entrada para a saída.

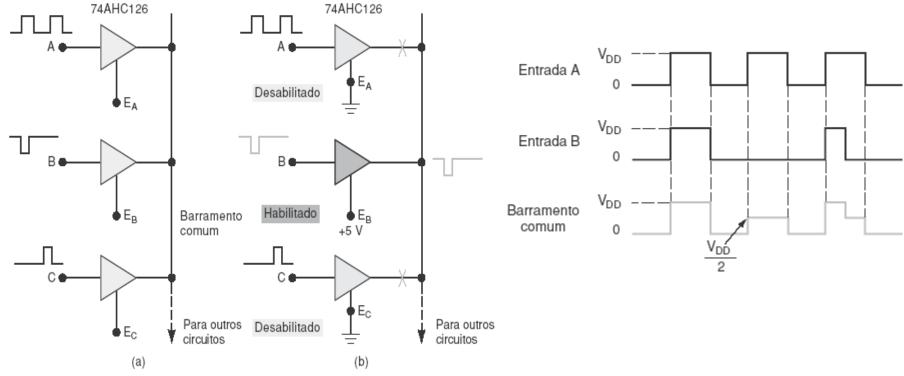

# **Compartilhando uma Via (Barramento)**

Na figura (a) qualquer um dos três sinais pode ser conectado à via, habilitando o buffer apropriado.

Na figura (b) (EB = 1, EA = EC = 0) mostra-se o sinal B conectado à via – demais saídas "desconectadas".

Contenção de barramento: Se duas saídas forem ativadas juntas, além da produção de correntes elevadas, a via terá um sinal de tensão na faixa indeterminada (quando em níveis diferentes).